Contador de cuatro bits decodificado a decimal que se

muestra en el DISPLAY 7 segmentos:

Hola a todos, en esta entrada os voy a enseñar cómo hacer un

contador de 4 bits decodificado a decimal y el cual vamos a reflejar en un

display 7 segmentos. Este proyecto es muy parecido al contador de 4 bits

anterior.

Bueno, como siempre, en primer lugar, nos vamos al entorno

de xilinx, y crearemos un nuevo proyecto,(file/ new Project), le pondremos el

nombre que queramos, yo lo llamo “contadorbcd7”, y elegimos la ruta donde

queremos guardarlo. Importante, como empezamos con el diseño, seleccionaremos

“schematich”.

Una vez creado el proyecto, añadiremos una nueva fuente,

como dije en anteriores proyectos, botón derecho en el proyecto y “new source”,

elegiremos “schematich” y le pondremos un nombre, yo aconsejo que sea el mismo

que el del proyecto, para saber siempre a qué proyecto pertenece ése archivo.

Bien, una vez nos aparezca la página en blanco, empezaremos

con el diseño de nuestro esquemático, para ello empezaremos introduciendo el

contador “CD4CE” y añadir un BUFG y un BUFGSR tanto a C como al CLK.

Será algo similar a esto.

Bueno, el siguiente paso es crear un nuevo símbolo, como

hicimos en el anterior contador, el cual será el decodificador de 7 segmentos. Para

esto tenemos que añadir una nueva fuente al proyecto, dándole al botón derecho

y seleccionando “new source”. Esta vez seleccionaremos “VHDL module”, en vez de

esquemático, y la pondremos un nombre, yo la he llamado “bcd7segmentos”.

Una vez

que le demos a ok, nos saldrá una ventana como esta.

Ahora es el momento de seleccionar las entradas y las

salidas del decodificador. Tenemos que tener en cuenta varias cosas, en primer

lugar, marcar en la dirección se es salida (out) o entrada (in), además,

debemos agregarle un nombre en la celda de “name” después, debemos marcar el

ticket en la casilla del bus y, por último marcaremos las 4 entradas ( de 0 a

3) y las 7 salidas (de 0 a 6). Tendrá que quedaros más o menos así.

Una vez le demos a ok nos generará un archivo VHDL. Este

tramo es algo más complicado, debido a que debemos introducirnos en el VHDL

para “configurar” nuestro decodificador. Sin embargo, el propio entorno xilinx

tiene un listado de plantillas que podemos que seleccionar.

Para eso tenemos que irnos a “edit” y seleccionamos

“language templates”, como os muestro en la imagen.

Una vez le demos deberemos ir a la siguiente ruta. VHDL/SYNTESIS CONSTRUCTS/CODING

EXAMPLES/MISC. Y una vez entremos

en misc, seleccionamos el que pone “7 segments display”, una vez lo

encontremos, tendremos que copiar tal cual ése código, para aplicarlo al

anterior VHDL. Cogeremos lo que os marco en el recuadro negro. Y lo pegaremos

en el anterior VHDL justo entre begin y end behavioral.

Bueno, ahora nos encontramos con una pequeña “trampa” por

decirlo de alguna manera, aunque aparentemente parezca una tontería, va a

determinar que el proyecto funcione. Tenemos que tener en cuenta el tipo de

led, esto es, como repaso del año pasado, los leds pueden ser de ánodo o cátodo

común, su diferencia es que uno se activa con un uno (ánodo) y el otro lo hace

con el 0 (cátodo). En términos claros,nuestra placa tiene leds de cátodo común,

por lo que vamos a tener que cambiar los 0 por 1 y los 1 por 0 para que esto

funcione.

Esto sería el equivalente a haberlo hecho para cátodo común.

Una vez cambiado eso, procederemos a “materializar” por

decirlo de alguna manera , lo que es el programa, dentro de un componente. Para

eso, seleccionamos “bcd7segmentos” y le damos, en la parte de la derecha a lo

que dice “create schematic symbol”. Una vez creado y encontrado en “symbols”,

tendremos que elaborar el esquemático del contador entero, más o menos es una

cosa así.

Recordad que para agregar etiquetas, extender cables y

nombrarlos, se hace mediante el uso de estos elementos en la barra superior de

herramientas. Como os enseño aquí.

Bueno, una vez acabado el esquemático es hora de empezar con

la simulación, el primer paso es crear una nueva fuente de tipo “test bench”,

es decir, botón derecho sobre el proyecto, new source, y a continuación

elegimos un nombre y marcamos el tipo, “test bench waveform”. Una vez le demos

a OK, deberemos elegir los parámetros como os muestro en ésta imagen.

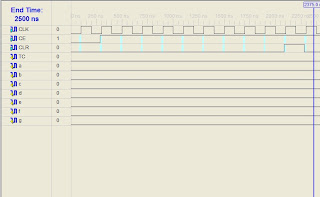

Entonces, tras darle a finish en esta ventana nos saldrá la

simulación, como os muestro a continuación.

Ya tendríamos nuestra simulación, sin embargo, como os dije

en anteriores proyectos, esta no es la verdadera simulación, porque no tiene en

cuenta todos los retrasos, por lo que no es tan precisa como la del “post fit”, para acceder a esa simulación

solo tenemos que ir a donde pone “simúlate post fit model” en la ventana de

procesos. Recordad que antes hay que configurarlo a 2500 ns, para que se nos

muestre el ciclo entero, para eso sólo tenemos que dar botón derecho sobre

“simúlate post fit model” y en

propiedades, cambiar la que nos sale por defecto, que suele ser 1000 ns.

Le daremos y nos deberá salir algo como esto.

Cuando ya tengamos el post fit simulado será hora de crear

el archivo con extensión ucf que, si recordáis de otros proyectos, es donde se

colocan todas las salidas y las entradas en el CPLD físico. Para crear el

archivo ucf, vamos a nuestro proyecto, botón derecho, new source, y después

elegiremos “implementation contraints file”, pondremos el nombre “contabcdufc”

y le daremos a OK, una vez hayamos hecho esto, se nos tendrá que haber creado

en la ventana de implementación.

Ya cuando le demos doble click sobre el UCF se nos abrirá el

entorno “PACE” y entonces podremos colocar las respectivas entradas y salidas

en el CPLD.

Importante, el CLR no se toca, el propio CPLD lo integra en

el pin 74.

Otra cosa a tener en cuenta es el CE, el cual es un enable, que debemos tener siempre activado para que nuestro contador funcione, de otra manera no lo hará.

Muy IMPORTANTE, no cometais el mismo error que yo, pensé que podría colocar los pines a mi antojo, puesto que la placa entrenadora que he usado tiene muchas de sus conexiones internas, sin embargo, precísamente por eso cometí el error, coloqué las salidas en los pines que me dió la gana, sin tener en cuenta que cada pin está asignado de una determinada manera al display, es decir, el PIN que representa a "a" debe ir colocada a p26, puesto que la placa microcontroladora está conectada intermanente de ese modo. Otra cosa a tener en cuenta es el CE, el cual es un enable, que debemos tener siempre activado para que nuestro contador funcione, de otra manera no lo hará.

Una vez los tengamos colocados, cerraremos la ventana y

daremos al Translate, así como que

nos genere el “fit”.

Para que todo esté en orden debemos tener la ventana de

procesos con todos los tickets verdes, de otra manera no nos funcionará nada.

Esto es todo que os sirva de mucha ayuda!

DESCARGAR PROYECTO AQUÍ

No hay comentarios:

Publicar un comentario